After dominating the electronics industry for decades, conventional silicon-based transistors are gradually approaching their limits, which is preventing engineers from further reducing their size without affecting their performance. To continue advancing portable computers, smart phones and other devices, researchers have thus been exploring the potential of transistors based on two-dimensional (2D) materials.

Researchers at Penn State University (PSU) led by Dr. Saptarshi Das, Ackley Professor of Engineering Science and Mechanics have developed high performance p-type field effect transistors (FETs) based on 2D materials. These transistors, introduced in a paper published in Nature Electronics, were created via a fabrication strategy that leverages the doping and thickness control of two 2D materials, namely molybdenum diselenide (MoSe2) and tungsten diselenide (WSe2).

“To overcome the limitations of silicon-based semiconductors and sustain progress, the industry must transition to alternative, sustainable semiconductors,” Mayukh Das, first author of the paper, told Phys.org. “One promising candidate is 2D transition metal chalcogenides (TMDs), which offer the potential for achieving high computational efficiency while maintaining low energy consumption.”

Silicon has highly tunable properties, which are particularly advantageous for the development of electronics. By introducing impurities, a process known as doping, transistors based on silicon can be made electron-deficient (p-type) or electron-rich (n-type), enabling the creation of complementary logic circuits.

“Metal-oxide-semiconductor field-effect transistors (MOSFETs), form the backbone of modern computing through complementary metal-oxide-semiconductor (CMOS) technology,” said Das.

“However, replicating CMOS logic using 2D TMDs presents a significant challenge: the absence of good p-type 2D MOSFET comparable to their n-type counterparts. Unlike silicon, which can be chemically tailored through doping, 2D TMDs inherently exhibit either n-type or p-type characteristics in their pristine form owing to pinning of metal Fermi level near the conduction or valance band edge.”

Although engineers have developed various highly performing n-type transistors based on 2D TMDs, p-type transistors based on these materials have not yet achieved comparable performances. This discrepancy in performance has so far hindered the large-scale use of these transistors for developing microelectronic devices.

“Addressing this challenge is critical to enabling the transition from silicon to 2D TMDs, meeting the demand for power-efficient, high-performance computation in an era increasingly driven by artificial intelligence (AI),” said Das.

“This pressing need motivated our research. Instead of waiting for the discovery of a high-performing p-type 2D TMD, we pursued a practical design strategy by employing substitutional doping—a proven method for enhancing electrical performance.”

The team adapted doping-based design strategies, applying them to the fabrication of p-type FETs based on 2D materials. To boost the performance of their p-type FETs, the researchers reduced a parameter known as the contact resistance (RC), which is known to degrade the current in the transistors while they are in the ON state.

“A strategy of degenerate substitutional doping selectively near the contacts has been commonly implemented in Si-based transistors to cut down on RC,” explained Das.

“The comparatively undoped or less doped body of the Si device helped to attain good electrostatic control, i.e. good ON/OFF ratio. However, the method of spatially doping certain regions in the transistor channel is possible only in bulk Si devices.”

Spatially doping some regions of channels in transistors based on TMDs is challenging. As compared to silicon, these materials are comprised of stacked layers of atoms. To create their transistors, the researchers first tried to devise a new strategy that would allow them to do this.

“In our high-performance p-type MOSFETs (Metal-oxide-semiconductor FETs), we circumvent these challenges using a uniformly doped 2D TMD channel (Nb-doped MoSe2 crystal) and by tuning up its doping efficacy near the channel-contact interfaces in comparison to the mid-channel region,” said Das.

“The high effective doping near the contacts allows easy carrier injection into the channel, resulting in high ON current in the transistor, while the less effective doping in between the contacts maintains good electrostatic control in the 2D MOSFET device.”

As a result of their underlying design, the MOSFETs fabricated by the researchers have a high ON current and can also be switched ON and OFF easily. The channel in the transistors is made of multilayered Nb-doped MoSe2, a 2D semiconducting TMD.

“Multilayered TMDs are uniquely different from their bulk form in the aspect that there are no true chemical bonds (out of plane) between two adjacent atomic layers,” said Das. “Instead, two adjacent layers are held together by weak van der Waals forces which allow seamless stacking of multiple monolayer films on top of each other.”

To implement their new design strategy, the researchers leveraged a phenomenon known as quantum confinement. This effect typically reduces the efficacy of dopants in multilayer TMDs with few stacked atomic layers (i.e., 1–3), compared to the same material with more stacked layers (i.e., 4–6).

“This phenomenon was substantiated by density functional theory (DFT) simulation of MoSe2 energy band structure when it is degenerately doped with p-type dopant Nb,” said Das.

“Based on the understanding from these simulations, we proposed our unique MOSFET design which has thick (4–6 layers) channel regions beneath the contacts for reduced contact resistance and thin (1–3 layers) channel regions in between the source and drain contacts for a reduced doping effect.”

The approach utilized by this team of researchers not only reduces RC but also boosts their transistors’ electrostatic gate control, which translates into the good ON/OFF and high ON currents observed. The Nb-doped MoSe2 layers in their transistors were grown via a method known chemical vapor transport (CVT) method, which was developed by the team’s collaborator Dr. Sofar Zdenek at the University of Chemistry and Technology in Prague.

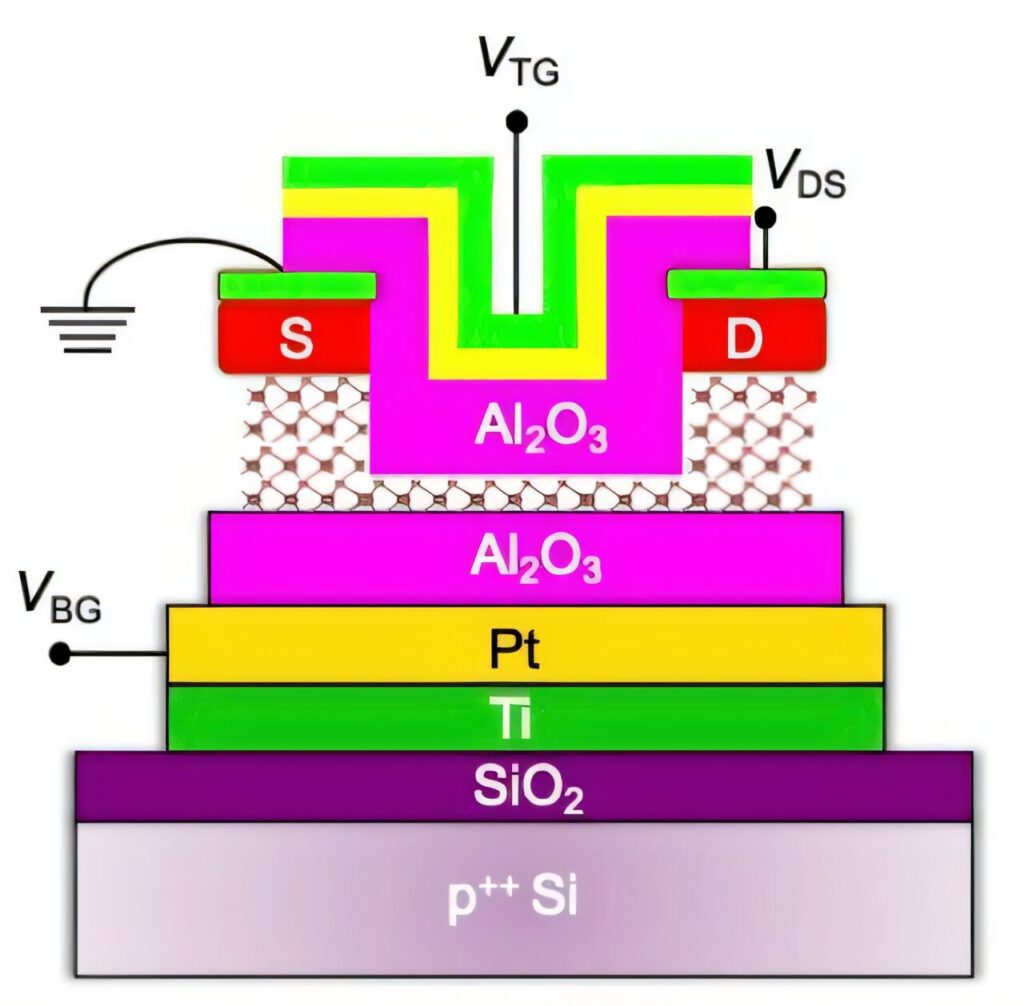

“To fabricate these devices, we exfoliated thick crystals (4–6 layers) of these Nb-doped MoSe2 on a back gate substrate with 50nm Al2O3 as the dielectric,” said Das.

“After defining the contacts by e-beam lithography, we deposited Pd contact metal on the doped MoSe2 by E-beam evaporation to form the devices. The devices were then exposed to mild oxygen plasma treatment to oxidize the topmost MoSe2 layer to MoOX—an oxide of Mo which is soluble in water.”

The region under the contacts in the transistors was protected from the plasma treatment and thus did not become oxidized. The researchers then washed away the remaining MoOX in their device by rinsing it in deionized water.

“This step of oxygen plasma treatment followed by DI water was repeated several times to thin down the mid channel region and achieve our proposed MOSFET structure,” explained Das. “Note that each oxygen plasma treatment step selectively removed only one atomic layer of the TMD channel. Using this strategy, we were able to achieve an On-current of 85 µA/um with an ON/OFF ratio of 104.”

The team combined the new design strategy they developed with well-known methods to boost the performance of the devices. For instance, they scaled the channels in the transistor’s combined dual-gate geometry and work function engineering. This allowed them to achieve an even higher ON-current of 212 µA/um, which is among the largest reported number for 2D p-type FETs.

“This involved fabricating a 50nm scaled channel device on a 25nm Al2O3 back gate oxide followed by oxygen plasma treatments to implement our design of thicker contact regions and thinner mid-channel regions,” said Das.

“Further fabrication steps involving ALD deposition of 20nm Al2O3 as a top gate dielectric and E-beam evaporation of Ni to form the top gate contacts. The top gate contact metal Ni and back gate contact metal Pt were chosen because of their high work function.”

When applied to 2D TMDs, the new doping strategy used by this team of researchers overcomes the limitations of previously introduced and well-established doping methods. Ultimately, it enables a good carrier injection and greater electrostatic control over the materials.

“A unique aspect of our design strategy is that this can be implemented to fabricate both high performing n-FETs as well not just p-FETs,” said Dipanjan Sen, co-first author of the paper.

“Just switching the p-type dopant Nb with a n-type dopant atom in the same device architecture will result in a high-performance n-type MOSFET. The fabrication process, including the mid-channel layer reduction oxygen plasma step, is simple and has enough merits in realizing circuit level demonstrations of complementary n- and p-type MOSFETs.”

The transistor design and doping strategy introduced by the team could contribute to the development of faster and more energy-efficient electronic circuits based on 2D semiconductors. The p-type MOSFETs created using their approach have already achieved a remarkable ON-current value of 212 µA/um at an ON/OFF ratio of 104, which could be further improved in the future.

“Our work also upholds the importance of considering multilayered 2D TMD films as a channel material for future 2D material-based electronics as a counter alternative to monolayered TMD materials,” said Sen.

“In the future, it could also encourage more research towards growth of doped 2D TMD large area films by advanced growth methods such as chemical vapor deposition (CVD) and metalorganic chemical vapor deposition (MOCVD).”

In their next studies, the researchers also plan further improvement of the scalability of their transistors. For instance, they could use large area CVD-grown multilayered 2D TMD materials, as opposed to exfoliated flakes.

“These future efforts would help us make circuits using these p-type MOSFETs,” added Das.

“There is a challenge of the extent of dopant incorporation in the 2D TMD lattice during large area CVD growth which requires substantial optimization. Other challenges such as threshold engineering, device to device variation invite substantial efforts from device research. Minimizing device to device variation could also help to achieve logic circuit demonstrations using these transistors.”